Article

Brief

This is the project that I am developing now during my master's degree.

Abstract

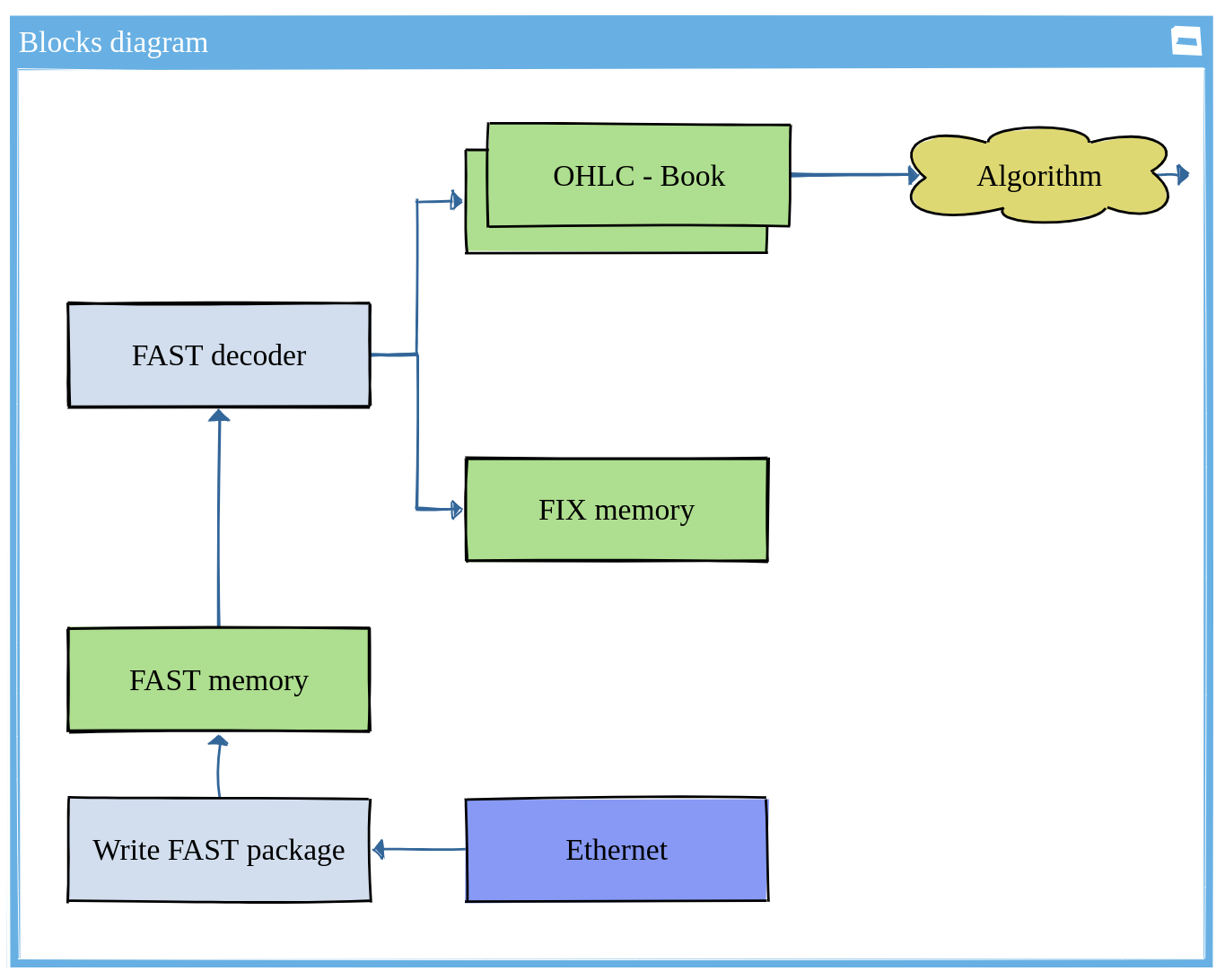

With the ever-increasing volume of data associated with the financial market, there is a growing need for fast and flexible computing solutions. Among the various forms of trading in the market, High-Frequency Trading (HFT) systems require high computational power for real-time trading and data analysis. This work implements the modules needed to decode messages following the FIX and FAST protocol, currently adopted by the B3 stock exchange. The modules will be implemented in FPGA-based hardware with parameterization capability to control market data format and data type.

Objective

The objective of this work is to develop a FPGA hardware architecture, that is compatible with the FAST 1.1 standard, which can be parameterized to receive data from the financial market. The hardware parameterization should reflect the user's settings concerning the desired properties of the data to optimize the hardware resources necessary for the implementation of the components in FPGA.

Methodology and Partial Results

I am developing a software version in C language of the components of the engine. I now have a version that can read a binary file containing a FAST message's log, decode to FIX messages, and generate an order book. The next step is to do a performance evaluation os the modules that compose the software and evaluate the viability of to hardware accelerate these modules. The High-Level Syntheses (HLS) tool from Intel, the Intel HLS, will be used to accelerate the modules.